## STG 2000 rev. C

## **MULTIMEDIA ACCELERATOR**

## PRELIMINARY INFORMATION

#### **KEY FEATURES**

- Single-chip Multimedia Accelerator

- Support for Industry Standards

- Acceleration for all DirectX API's under Windows 95

- Industry-leading GUI Acceleration

- Full-Motion Video Acceleration (Indeo, MPEG, Cinepak)

- Real-Time Texture Mapped 3D Graphics

- Accelerates All 3D Standards: triangles, quadrilaterals and curves

- Hardware Audio WaveTable Synthesis

- **Enhanced Digital Game Port**

- System level performance and cost optimization

## DESCRIPTION

grated VGA for DOS.

provides support for legacy applications with full multimedia drivers for Windows 3.11 and an inte-

## **BLOCK DIAGRAM**

April 1996 42 1653 04

7929237 0081581 463

## **TABLE OF CONTENTS**

| 1  | DEV   | ICE PINOUTS                                   |

|----|-------|-----------------------------------------------|

|    | 1.1   | STG2000 PCI DRAM PIN-OUT                      |

| 2  | PIN I | DESCRIPTIONS                                  |

|    | 2.1   | PCI BUS INTERFACE                             |

|    | 2.2   | DRAM MEMORY INTERFACE                         |

|    | 2.3   | EEPROM INTERFACE                              |

|    | 2.4   | DISPLAY INTERFACE                             |

|    | 2.5   | AUDIO CODEC INTERFACE                         |

|    | 2.6   | DEVICE ENABLE SIGNALS                         |

| 3  | OVE   | RVIEW OF THE STG2000                          |

|    | 3.1   | SINGLE-CHIP ACCELERATOR FOR ALL OF WINDOWS 95 |

|    | 3.2   | STANDARDS ACCELERATION                        |

|    | 3.3   | REAL TIME TEXTURE MAPPED 3D GRAPHICS          |

|    | 3.4   | HARDWARE AUDIO WAVETABLE SYNTHESIS ENGINE     |

|    | 3.5   | DIGITAL GAMEPORT ENGINE                       |

|    | 3.6   | HIGHEST OVERALL SUBSYSTEM PERFORMANCE         |

|    | 3.7   | LOWEST OVERALL SUBSYSTEM COST                 |

|    | 3.8   | SCREEN RESOLUTIONS                            |

|    | 3.9   | ADVANCED SEMICONDUCTOR PROCESS                |

|    |       | HIGH-PERFORMANCE MULTIMEDIA SUBSYSTEM         |

|    | 3.11  | REFERENCE DESIGN KIT                          |

|    |       | SOFTWARE DEVELOPMENT KIT                      |

| 4  |       | T BUS INTERFACES                              |

|    | 4.1   |                                               |

| 5  | MEM   | ORY AND PALETTE-DAC INTERFACE                 |

|    | 5.1   | DRAM MEMORY INTERFACE                         |

|    | 5.2   | ROM INTERFACE                                 |

|    | 5.3   | EEPROM INTERFACE                              |

|    | 5.4   | PALETTE-DAC INTERFACE                         |

| _  | 5.5   | ALTCS# INTERFACE                              |

| 6  |       | IO CODEC INTERFACE                            |

|    |       | AUDIO CODEC INTERFACE TIMING SPECIFICATION    |

| 7  |       | ER-ON RESET CONFIGURATION                     |

| 8  |       | CTRICAL SPECIFICATIONS                        |

|    |       | ABSOLUTE MAXIMUM RATINGS                      |

|    | 8.2   | DC SPECIFICATIONS                             |

|    | 8.3   | OPERATING CONDITIONS                          |

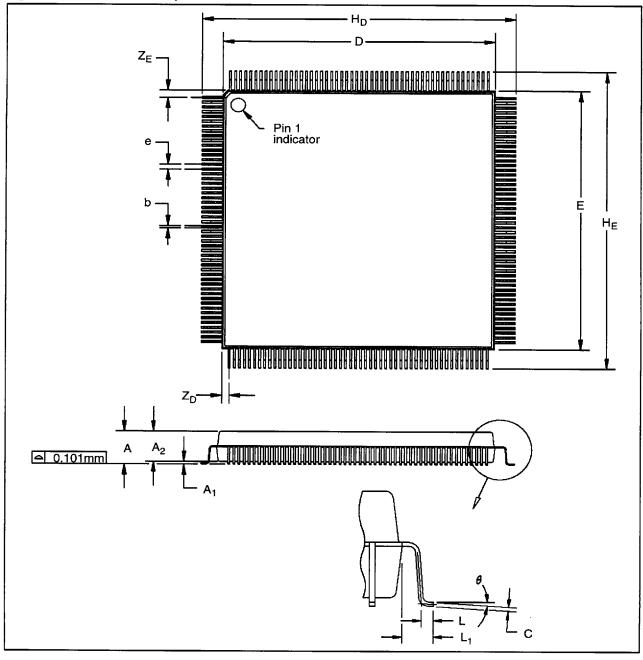

| 9  | PACI  | KAGE DIMENSION SPECIFICATION                  |

|    | 9.1   | 208 PIN PLASTIC QUAD FLAT PACK                |

| 10 | REFE  | ERENCES                                       |

| 11 | ORD   | ERING INFORMATION                             |

|    |       | ENDICES                                       |

| Α  |       | CONFIGURATION REGISTERS                       |

|    | A.1   | REGISTER DESCRIPTIONS FOR FUNCTION 0 (VGA)    |

|    |       | REGISTER DESCRIPTIONS FOR FUNCTION 1 (NV)     |

|    |       |                                               |

|    |       |                                               |

## STG2000 rev. C

| В | GAN | IE PORT REGISTER               | 59 |

|---|-----|--------------------------------|----|

| С | MPU | -401 REGISTERS                 | 60 |

| D | VGA | REGISTERS                      | 61 |

|   |     | GENERAL REGISTERS              |    |

|   |     | SEQUENCER REGISTERS            |    |

|   | D.3 | CRT CONTROLLER REGISTERS       | 65 |

|   | D.4 | GRAPHICS CONTROLLER REGISTERS  | 73 |

|   | D.5 | ATTRIBUTE CONTROLLER REGISTERS | 77 |

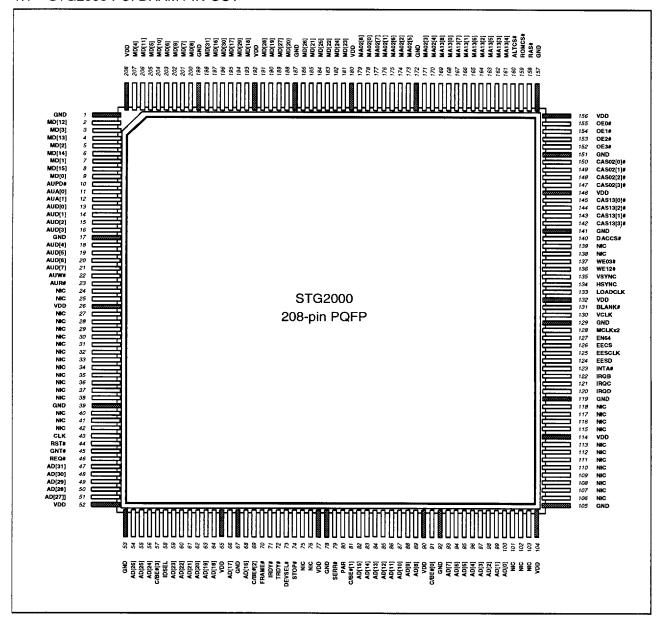

### 1 DEVICE PINOUTS

Power and ground pins are denoted by shading in the following diagram.

### 1.1 STG2000 PCI DRAM PIN-OUT

#### NOTES

- 1 NIC = No Internal Connection. Do not connect to these pins.

- 2 VDD=3.3V

## 2 PIN DESCRIPTIONS

## 2.1 PCI BUS INTERFACE

| Signal     | 1/0 | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |

|------------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| CLK        | 1   | PCI clock. This signal provides timing for all transactions on the PCI bus, except for RST# and INTA#. All PCI signals are sampled on the rising edge of CLK and all timing parameters are defined with respect to this edge.                                                                                                                                                                                                                                                                            |  |  |

| RST#       | 1   | PCI reset. This signal is used to bring PCI-specific registers, sequencers and signals to a consistent state. When <b>RST#</b> is asserted all PCI output signals are tristated.                                                                                                                                                                                                                                                                                                                         |  |  |

| AD[31:0]   | 1/0 | 32-bit multiplexed address and data bus. A bus transaction consists of an address phase followed by one or more data phases.                                                                                                                                                                                                                                                                                                                                                                             |  |  |

| C/BE[3:0]# | 1/0 | Multiplexed bus command and byte enable signals. During the address phase of a transaction C/BE[3:0]# define the bus command, during the data phase C/BE[3:0]# are used as byte enables. The byte enables are valid for the entire data phase and determine which byte lanes contain valid data. C/BE[0]# applies to byte 0 (LSB) and C/BE[3]# applies to byte 3 (MSB).                                                                                                                                  |  |  |

| PAR        | 1/0 | Parity. This signal is the even parity bit generated across AD[31:0] and C/BE[3:0]#. PAR is stable and valid one clock after the address phase. For data phases PAR is stable and valid one clock after either IRDY# is asserted on a write transaction or TRDY# is asserted on a read transaction. Once PAR is valid, it remains valid until one clock after completion of the current data phase. The master drives PAR for address and write data phases; the target drives PAR for read data phases. |  |  |

| FRAME#     | I/O | Cycle frame. This signal is driven by the current master to indicate the beginning of an access and its duration. <b>FRAME#</b> is asserted to indicate that a bus transaction is beginning. Data transfers continue while <b>FRAME#</b> is asserted. When <b>FRAME#</b> is deasserted, the transaction is in the final data phase.                                                                                                                                                                      |  |  |

| IRDY#      | 1/0 | Initiator ready. This signal indicates the initiator's (bus master's) ability to complete the current data phase of the transaction. IRDY# is used in conjunction with TRDY#. A data phase is completed on any clock when both IRDY# and TRDY# are sampled as being asserted. During a write, IRDY# indicates that valid data is present on AD[31:0]. During a read, it indicates that the master is prepared to accept data. Wait cycles are inserted until both IRDY# and TRDY# are asserted together. |  |  |

| TRDY#      | 1/0 | Target ready. This signal indicates the target's (selected device's) ability to complete the current data phase of the transaction. TRDY# is used in conjunction with IRDY#. A data phase is completed on any clock when both TRDY# and IRDY# are sampled as being asserted. During a read, TRDY# indicates that valid data is present on AD[31:0]. During a write, it indicates the target is prepared to accept data. Wait cycles are inserted until both IRDY# and TRDY# are asserted together.       |  |  |

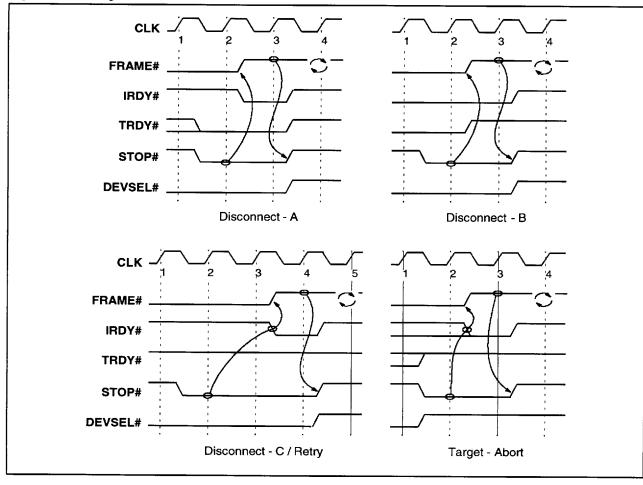

| STOP#      | 1/0 | <b>STOP#</b> indicates that the current target is requesting the master to terminate the current transaction.                                                                                                                                                                                                                                                                                                                                                                                            |  |  |

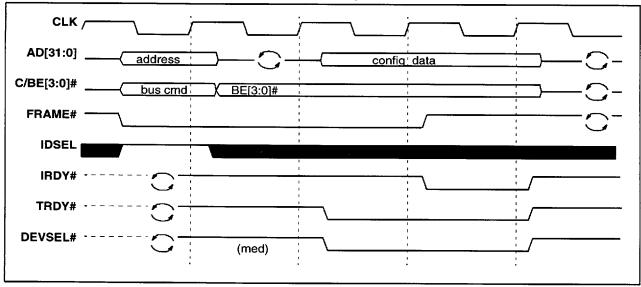

| IDSEL      | 1   | Initialization device select. This signal is used as a chip select during configuration read and write transactions.                                                                                                                                                                                                                                                                                                                                                                                     |  |  |

| DEVSEL#    | 1/0 | Device select. When acting as an output <b>DEVSEL#</b> indicates that the STG2000 has decoded the PCI address and is claiming the current access as the target. As an input <b>DEVSEL#</b> indicates whether any other device on the bus has been selected.                                                                                                                                                                                                                                              |  |  |

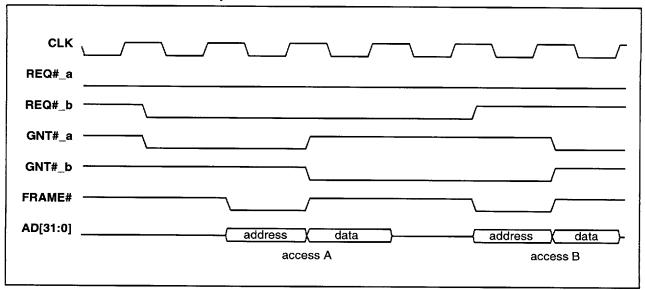

| REQ#       | 0   | Request. This signal is asserted by the STG2000 to indicate to the arbiter that it desires to become master of the bus.                                                                                                                                                                                                                                                                                                                                                                                  |  |  |

| GNT#       | ŀ   | Grant. This signal indicates to the STG2000 that access to the bus has been granted and it can now become bus master.                                                                                                                                                                                                                                                                                                                                                                                    |  |  |

|            |     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |

| Signal              | 1/0 | Description                                                                                                                                                                                                                             |

|---------------------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SERR#               | 0   | System error. This signal is used by the STG2000 to report parity errors and significant system errors. SERR# is pure open drain and is actively driven for a single PCI clock, the assertion of SERR# being synchronous to that clock. |

| INTA#               | 0   | Interrupt request line. This open drain output is asserted and deasserted asynchronously to <b>CLK</b> .                                                                                                                                |

| IRQB, IRQC,<br>IRQD | 0   | Interrupt Request Lines. These interrupt signals are active high, level triggered interrupts that may be connected to the IRQ lines on the ISA bus.                                                                                     |

## 2.2 DRAM MEMORY INTERFACE

| Signal                                       | 1/0                                                                   | Description                                                                                                                                                                                                                                                                                |  |

|----------------------------------------------|-----------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| MD[31:0] I/O                                 |                                                                       | The 32-bit memory data bus. MD[31:0] are also used to load pixel data into the Palette-DAC, MD[7:0] to access the 8-bit EPROM, MD[15:8] to access the Palette-DAC and MD[30:16] to address the 32KByte EPROM.                                                                              |  |

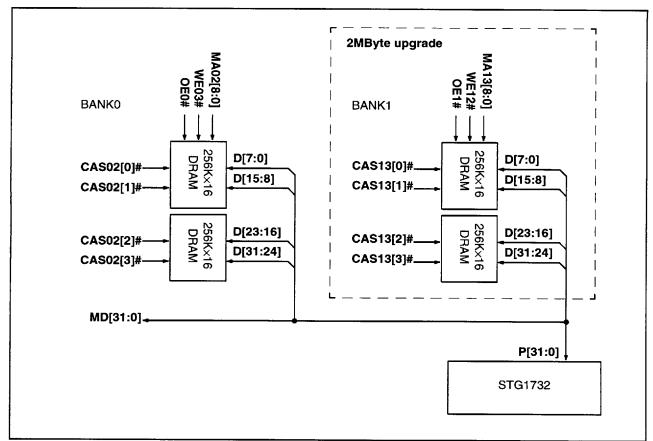

| MA02[8:0]                                    | 0                                                                     | Memory Address bus for DRAM banks 0 and 2. Supports symmetric address 256K x n memory architectures.                                                                                                                                                                                       |  |

| MA13[8:0]                                    | 0                                                                     | Memory Address bus for DRAM banks 1 and 3. Supports symmetric address 256K x n memory architectures.                                                                                                                                                                                       |  |

| RAS#                                         | 0                                                                     | Row Address Strobe for all memory banks.                                                                                                                                                                                                                                                   |  |

| CAS02[3:0]#                                  | 0                                                                     | Column Address Strobe for each byte in DRAM banks 0 and 2.                                                                                                                                                                                                                                 |  |

| CAS13[3:0]#                                  | 13[3:0]# O Column Address Strobe for each byte in DRAM banks 1 and 3. |                                                                                                                                                                                                                                                                                            |  |

| WE03# O Write Enable for DRAM banks 0 and 3. |                                                                       | Write Enable for DRAM banks 0 and 3.                                                                                                                                                                                                                                                       |  |

| WE12# O Write Enable for DRAM banks 1 and 2. |                                                                       | Write Enable for DRAM banks 1 and 2.                                                                                                                                                                                                                                                       |  |

| OE0#, OE1#,<br>OE2#, OE3#                    | 0                                                                     | Output Enable for each DRAM bank.                                                                                                                                                                                                                                                          |  |

| EN64                                         | 0                                                                     | This output is used in 2 and 4MByte framestores which interface to the STG1764. When high this pin tri-states external bus transceivers between two 32-bit interfaces to the 64-bit Pixel Port of the STG1764. When low this pin enables the connection between the two 32-bit interfaces. |  |

| MCLKx2                                       | 1                                                                     | Memory Clock x 2. This signal provides a timing reference to all internal functions of the STG2000. This clock is sourced from the STG1732/64 memory clock output. <b>MCLKx2</b> runs at twice the frequency of the internal memory clock.                                                 |  |

## 2.3 EEPROM INTERFACE

| Signal | 1/0 | Description                                                                                                                       |

|--------|-----|-----------------------------------------------------------------------------------------------------------------------------------|

| EECS   | 0   | EEPROM chip select. This signal requires an external 50K $\Omega$ pull-down to hold the EEPROM in a quiescent state during reset. |

| EESD   | 1/0 | EEPROM bidirectional data.                                                                                                        |

| EESCLK | 0   | EEPROM Clock. Data is clocked into/out of the 93C46A based on the rising edge of this clock as defined by the Microwire protocol. |

## 2.4 DISPLAY INTERFACE

| Signal                                                                                                                                                                             | 1/0                                                                                                                                 | Description                                                                                                                                                                                                                                                                                                 |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DACCS#  O Enables the Palette-DAC to be accessed via the data bus. This pin is us with MD[31:0] to load pixel data and MD[15:8] to access the Palette-DA                           |                                                                                                                                     | Enables the Palette-DAC to be accessed via the data bus. This pin is used in conjunction with MD[31:0] to load pixel data and MD[15:8] to access the Palette-DAC register.                                                                                                                                  |

| LOADCLK                                                                                                                                                                            | O Connects to the Palette-DAC LOADCLK pin. The rising edge of this signal coupling on the Palette-DAC LOADEN# and pixel input pins. |                                                                                                                                                                                                                                                                                                             |

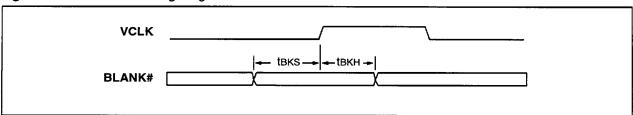

| BLANK#                                                                                                                                                                             | 0                                                                                                                                   | Blanking signal sampled by the Palette-DAC on the rising edge of VCLK. A '0' sampled will, after a pipeline delay, turn the DAC outputs off. A special protocol on the Palette-DAC BLANK# and VCLK pins enables the controller to reset various functions of the Palette-DAC at the start of frame flyback. |

| VCLK  I Video Clock. This clock is sourced from the Palette-DAC memory clock outpost frequency is the video frequency at the DACs divided by 1, 2, 4, 8, or 16, the selected mode. |                                                                                                                                     | Video Clock. This clock is sourced from the Palette-DAC memory clock output. The VCLK frequency is the video frequency at the DACs divided by 1, 2, 4, 8, or 16, depending on the selected mode.                                                                                                            |

| VSYNC O Vertical sync supplied to the display monitor. No buffering is required to d itor.                                                                                         |                                                                                                                                     | Vertical sync supplied to the display monitor. No buffering is required to drive a local monitor.                                                                                                                                                                                                           |

| HSYNC                                                                                                                                                                              | 0                                                                                                                                   | Horizontal sync supplied to the display monitor. No buffering is required to drive a local monitor.                                                                                                                                                                                                         |

## 2.5 AUDIO CODEC INTERFACE

| Signal   | 1/0 | Description                                                                                               |  |

|----------|-----|-----------------------------------------------------------------------------------------------------------|--|

| AUW#     | 0   | Audio Write command strobe.                                                                               |  |

| AUR#     | 0   | Audio Read command strobe.                                                                                |  |

| AUA[1:0] | 0   | Audio Address outputs.                                                                                    |  |

| AUD[7:0] | I/O | Audio Data bus. These pins transfer data and control information between the Audio Codec and the STG2000. |  |

| AUPD#    | 0   | Places the Audio Codec in its low power consumption mode.                                                 |  |

## 2.6 DEVICE ENABLE SIGNALS

| Signal | 1/0 | Description                                                                                                                                                                                                                                               |

|--------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ROMCS# | 0   | Enables reads from an external 32Kx8 EPROM or Flash ROM. This signal is used in conjunction with MD[7:0] for the ROM data bus, MD[30:16] for the 15-bit address, and MD[31] for the R/W# select.                                                          |

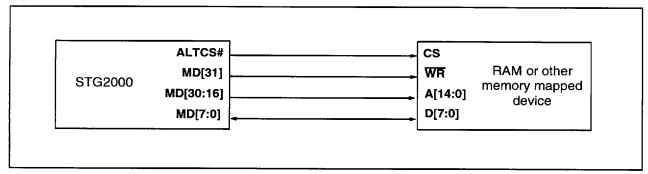

| ALTCS# | 0   | Allows an 8-bit external device with up to 32KBytes of address space to be accessed via the memory data bus. This signal is used in conjunction with MD[7:0] for an 8-bit data bus, MD[30:16] for the 15-bit address bus, and MD[31] for the R/W# select. |

#### 3 OVERVIEW OF THE STG2000

#### 3.1 SINGLE-CHIP ACCELERATOR FOR ALL OF WINDOWS 95

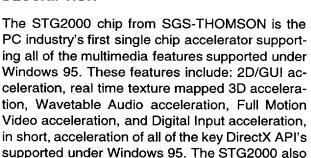

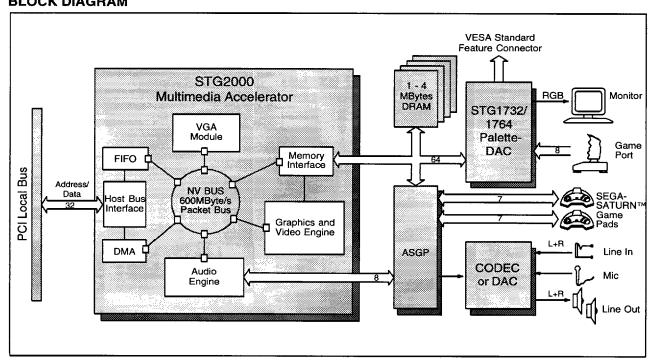

The STG2000 chip from SGS-THOMSON Microelectronics is the PC industry's first single chip accelerator supporting all of the multimedia features supported under Windows 95. These features include: 2D/GUI acceleration, real time texture mapped 3D acceleration, Wavetable Audio acceleration, Full Motion Video acceleration, and Digital Input acceleration, in short, acceleration of all of the key DirectX API's supported under Windows 95. The STG2000 also provides support for legacy applications with full multimedia drivers for Windows 3.11 and an integrated VGA for DOS.

This concurrent acceleration is achieved through individual hardware engines within the chip connected by a 600MByte/s data bus. These hardware engines provide functionality that would have required 3 separate PC cards in the past. Combining the engines in one chip not only eliminated the cost of the multiple cards, more importantly, it enabled resources to be optimized at a system level among the separate engines. A total of 1MByte of framebuffer memory is all that is required to obtain high performance with all of the concurrent engines. The rest of the required resources such as texture memory and audio wave samples, are DMA'd from system memory using the on chip bus mastering DMA engine.

The combination of single chip solution and high performance using minimal memory results in the lowest cost yet highest performance Windows 95 accelerator in the market today.

# Goals: Better, Faster, Lower Cost, Accelerate Today's Standards

The design goals for the STG2000 chip were to create a complete multimedia solution that was: lower cost, higher performance, greater functionality and yet capable of being a drop-in replacement for today's standard GUI accelerators. As such, all of the functionality in today's graphics accelerator chips are included in the STG2000. However the STG2000 is unique in that all of the other key components in today's Interactive Multimedia PC have also been incorporated into the same chip. This means that functionality such as real-time texture mapped 3D graphics, Wavetable Audio, Digital Gameport, and Full Motion Video Acceleration, are all concurrently hardware accelerated on a single piece of silicon. This integration of

functionality permits highly efficient allocation of system resources so that a single megabyte of framebuffer memory can be shared among all of the hardware engines on the chip thereby ensuring low cost. This encapsulated multimedia subsystem functionality enables STG2000 to be the industry's first complete DirectX accelerator, accelerating all the pieces of Microsoft's DirectX API's. The STG2000 chip provides breakthrough levels of functionality, performance, low cost, and differentiation for the PC marketplace.

#### **KEY Features**

- · Single-chip Multimedia Accelerator

- Support for Industry Standards

- Acceleration for all DirectX API's under Windows 95

- Industry-leading GUI Acceleration

- Full-Motion Video Acceleration (Indeo, MPEG, Cinepak)

- Real-Time Texture Mapped 3D Graphics

- Accelerates All 3D Standards: triangles, quadrilaterals and curves

- Hardware Audio WaveTable Synthesis

- Enhanced Digital Game Port

- System level performance and cost optimization

#### 3.2 STANDARDS ACCELERATION

#### **Direct-X Acceleration Under Windows 95**

The STG2000 chip incorporates functionality that directly accelerates today's leading API standard, Microsoft's Windows 95 DirectX API's. It is currently the only device on the market today that can concurrently hardware accelerate DirectDraw, DirectVideo, Direct3D, DirectSound, and DirectInput. As content developers migrate to this set of API standards, STG2000 designs will be poised to provide the complete acceleration solution.

- DirectDraw/DirectVideo Hardware 2D/GUI/ Video engine

- Direct3D Hardware real time 3D texture mapping engine

- DirectSound Hardware digital mixing no CPU overhead

- DirectInput Digital Gameport supports standard PC joysticks and SEGA™ peripherals

8/81

SGS-THOMSON

#### **GUI Acceleration Under Windows 95**

- Extensive support for Microsoft's DirectDraw API

- Optimized for multiple color depths including 8, 15, 24, and 30 bits per pixel

- Hardware color dithering higher quality with less framebuffer usage

#### **Full-Motion Video Acceleration**

The STG2000 graphics engine accelerates fullmotion video playback and can sustain 30 frames per second of true-color digital video. Hardware video acceleration provides image enhancement and scaling of video streams to full-screen display.

- Support for DirectVideo in Windows 95

- · Video interpolation for enhanced image quality

- Integration of graphics and video enabling special effects

- Accelerated playback of industry standard CO-DECs such as MPEG, Indeo, and Cinepak

- · Interframing for reduced flicker

# 3.3 REAL TIME TEXTURE MAPPED 3D GRAPHICS

The STG2000's 3D Graphics engine was architected from inception for consumer interactive multimedia. The resulting price goals drove the design of a graphics engine that maintains its high performance with minimal framebuffer memory requirements. The STG2000 is able to maintain its high performance in only 1MByte of framebuffer memory.

Consumer multimedia also dictated that the STG2000 was designed to accelerate consumer style 3D graphics. It's optimization focuses on delivering the highest possible frame rate for the maximum in interactivity. This optimization is evident on games like Virtua Fighter Remix™, which is a 640x400, 16 bits per pixel game that runs at greater than 30 frames per second. To put it in perspective, on today's 133MHz Pentiums without acceleration, it is only possible to run similar games at 320x200, 8 bits per pixel at 20fps.

Some key capabilities of the 3D engine are:

- High performance acceleration of perspectivecorrect textured triangles, quadrilaterals, and curves

- Highest rendering pixel rate for fastest 3D frame rate

- Photorealistic 3D texture mapping, including lighting, fog, transparency, etc.

- Video Texturing ability to treat video as a texture. Allows user to map video onto 3D objects.

### 3.4 HARDWARE AUDIO WAVETABLE SYN-THESIS ENGINE

The STG2000 chip integrates a high performance audio engine to deliver the highest fidelity and realism for today's interactive multimedia applications. With support for dynamic downloadable samples, developers can utilize custom samples for exciting sound and MIDI effects. Additionally, the NV Architecture's native synchronization capability allows developers to precisely control the relationship of audio playback to 3D graphics, video, or other audio streams. This capability is necessary for a truly interactive experience.

For the system integrator, the STG2000's audio solution allows multiple options on how to implement the audio subsystem. These options offer solutions at various pricepoints and integration levels depending on which of the possible audio interfaces is desired.

- Support for industry audio standards:

- Windows 95 DirectSound API

- MPU-401, General MIDI, Miles Audio Interface Library (AIL), HMI Sound Operating System (SOS)

- Hardware 350MIPS Audio Engine supporting 32 channels of 16-bit wavetable sound

- Concurrent playback and hardware mixing of up to 50 channels of digital audio

- Downloadable Wavetable samples stored in system memory instead of dedicated ROM/ RAM

- Support for effects such as tremolo, vibrato and portamento

- Support for industry standard I<sup>2</sup>S interface

## 3.5 DIGITAL GAMEPORT ENGINE

The STG2000 is the first product to feature an IBM compatible digital game port as well as two SEGA-SATURN™ peripheral ports. Where standard game ports demand the near-constant intervention of the PC's microprocessor, STG2000's digital game port DMA-bursts the joystick's position without interrupting the processor. The benefit is better overall system performance, a crucial advantage in multimedia applications. The STG2000 game

port also provides higher resolution and sampling rates than standard game ports, enabling a finer degree of joystick control and quicker response to user actions.

Another key advantage of the digital gameport is that it allows a multitude of accessories and functionality not possible on the PC before. Two players can now simultaneously compete using the 2 SEGA<sup>TM</sup> ports available on every STG2000 card. Up to six players can concurrently participate in multiplayer titles using the optional multi-tap device also supported by this port.

- All gaming ports are supported in Microsoft's DirectInput API

- 8-channel digital game port with advanced analog/digital sampler

- 13-bit capture resolution with sample rates up to 92Hz (versus a typical game port of 8-bit resolution and 1Hz sample rate)

- Support for SEGASATURN™ peripherals

- Bus mastering DMA frees up to 12% of a Pentium class CPU's bandwidth

### 3.6 HIGHEST OVERALL SUBSYSTEM PER-FORMANCE

The STG2000 chip was not designed as a single independent entity. The surrounding components were all taken into account in the performance optimizations that took place. This concept of system performance vs. single chip performance, has always been practiced in the game console industry. That industry has always realized that it is no good just having great graphics, if audio or gameport or video holds back the final application's performance. That is the main reason why PC titles were never capable of achieving the quality of the top 3D console box titles.

Until now, the solutions in the PC industry have always been fragmented and independent. The software developer, for example, had no idea what Sound card is coupled with which 3D card, and therefore has always had to program to the lowest common denominator, sacrificing overall frame rate and title quality.

The STG2000 is the PC industry's first self contained multimedia subsystem. Knowing the performance of all available components ensures consistently high performance throughout the entire subsystem. This allows the STG2000 to power the leading titles with the highest possible frame rates.

#### 3.7 LOWEST OVERALL SUBSYSTEM COST

There are usually two main components in the cost of a multimedia subsystem. The cost of the media accelerator chips themselves, and the cost of the memory associated with the individual media accelerators. By integrating the key media types into a single chip, SGS-THOMSON Microelectronics allows the board/system integrator to provide the full consumer interactive multimedia experience in a single low cost card.

Perhaps more importantly, the integration of the various media accelerators allowed for system level optimization of memory resources. Traditionally, the 2D card would have required frame buffer memory (1-2MByte), the 3D card requires Z buffer, and texture memory (2-4MByte) and the Audio card requires even more memory for storing wavetable samples (1-4MByte).

In the STG2000 subsystem, only 1MByte of framebuffer memory is necessary to support the combination of 2D, Video, 3D, and Wavetable Audio. The unique hardware architecture combined with PCI bus mastering DMA capabilities allows the STG2000 chip to store wavetable samples, and 3D texture maps in system memory, resulting in the lowest possible memory requirements. This combination of chip integration and memory integration results in the lowest overall system cost.

#### 3.8 SCREEN RESOLUTIONS

Screen resolutions and refresh rates supported by the STG1764 135MHz 64-bit Palette-DAC with 2MBytes of DRAM include:

| Pixel | Resolutions and refresh rate supported |             |              |              |               |  |

|-------|----------------------------------------|-------------|--------------|--------------|---------------|--|

| depth | 640×<br>480                            | 800×<br>600 | 1024×<br>768 | 1152×<br>864 | 1280×<br>1024 |  |

| 8     | 96Hz                                   | 96Hz        | 96Hz         | 96Hz         | 75Hz          |  |

| 15    | 96Hz                                   | 96Hz        | 75Hz         | 70Hz         |               |  |

| 24/30 | 96Hz                                   | 75Hz        |              |              |               |  |

## 3.9 ADVANCED SEMICONDUCTOR PRO-CESS

The STG2000 is manufactured on SGS-THOM-SON's advanced 0.5 micron, 3 layer metal, 3.3V process with SURE 6 quality and reliability standards. The low power dissipation and reduced output switching noise significantly increases system reliability. Output drivers are 5V-tolerant process compensated for PCI compatibility.

10/81

# 3.10 HIGH-PERFORMANCE MULTIMEDIA SUBSYSTEM

The STG2000 Multimedia Accelerator brings together an unrivaled level of multimedia functionality which previously required dozens of components and multiple PCBs. Typical parts count for 1 and 2MByte DRAM implementations includes the following active components:

| Active component               | 1MByte | 2MByte |

|--------------------------------|--------|--------|

| STG2000 Multimedia Accelerator | 1      | 1      |

| STG1764 Palette-DAC            | 1      | 1      |

| SEGA™ interface ASIC           | 1      | 1      |

| 256Kx16                        | 2      | 4      |

| Audio DAC                      | 1      | 1      |

| EPROM                          | 1      | 1      |

| EEPROM                         | 1      | 1      |

| Dual Op-Amp                    | 2      | 2      |

| Total                          | 10     | 12     |

#### 3.11 REFERENCE DESIGN KIT

A Reference Design Kit (RDK) is available for the STG2000. This includes all necessary information required to design and manufacture a family of

high performance PC Multimedia Accelerator Cards based on the STG2000 with different memory options.

#### The RDK includes:

- STG2000 and STG1764 Palette-DAC Databook

- A detailed DESIGN GUIDE

- Options for using SoundBlaster™ compatible CODECs

- 1 and 2MBytes DRAM board design and schematics

- Bill of Materials and a device cross reference

- Gerber/Aperture/Drill files for turnkey board production

- BIOS, BIOS modification utilities, device drivers, and diagnostics

### 3.12 SOFTWARE DEVELOPMENT KIT

A Software Development Kit (SDK) (which includes header files, sample code, manuals, and on-line documentation) is available for Developers taking advantage of the capabilities of NV Architecture or using NVLIB.

#### 4 HOST BUS INTERFACES

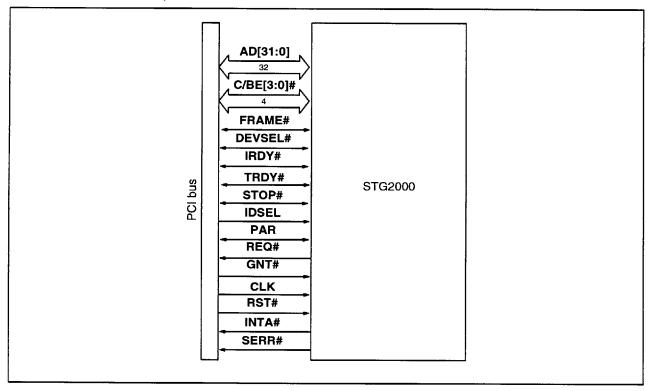

### 4.1 PCI BUS INTERFACE

## **PCI** capability

The STG2000 supports a glueless interface to PCI (2.0) with both master and slave capabilities. The host interface is fully compliant with the 32-bit PCI (2.0) specification.

The Multimedia Accelerator supports operation up to 33MHz with zero-wait state capability for bursts exceeding 128 bytes and full bus mastering capability handling 32-byte burst reads and 16-byte burst writes.

Figure 1. PCI interface pin connections

Table 1. PCI bus commands supported by the STG2000

| Bus master            | Bus slave                    |    |

|-----------------------|------------------------------|----|

| Memory read and write | Memory read and write        |    |

| Memory read line      | I/O read and write           |    |

|                       | Configuration read and write |    |

|                       | Memory read multiple         |    |

|                       | Memory read line             | ** |

|                       | Memory write invalidate      |    |

## **PCI timing parameters**

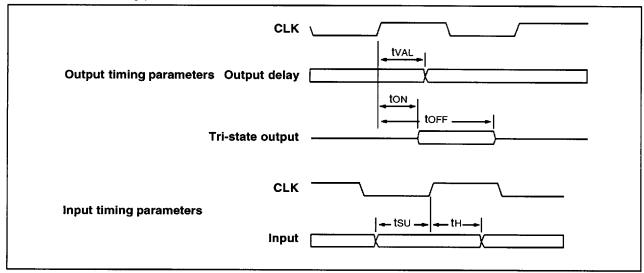

The timing specification of the PCI interface takes the form of generic setup, hold and delay times of transitions to and from the rising edge of **CLK** as shown in Figure 2.

Figure 2. PCI timing parameters

Table 2. PCI timing parameters

| Symbol                | Parameter                                  | Min. | Max. | Unit | Notes                                  |

|-----------------------|--------------------------------------------|------|------|------|----------------------------------------|

| tVAL                  | CLK to signal valid delay (bussed signals) | 2    | 11   | ns   | 1                                      |

| tval <sup>(PTP)</sup> | CLK to signal valid delay (point to point) | 2    | 12   | ns   | 1                                      |

| ton                   | Float to active delay                      | 2    |      | ns   | ······································ |

| toff                  | Active to float delay                      |      | 28   | ns   |                                        |

| tsu                   | Input set up time to CLK (bussed signals)  | 7    |      | ns   | 1                                      |

| tsu <sup>(PTP)</sup>  | Input set up time to CLK (GNT#)            | 10   |      | ns   | 1                                      |

| tH                    | Input hold time from CLK                   | 0    |      | ns   |                                        |

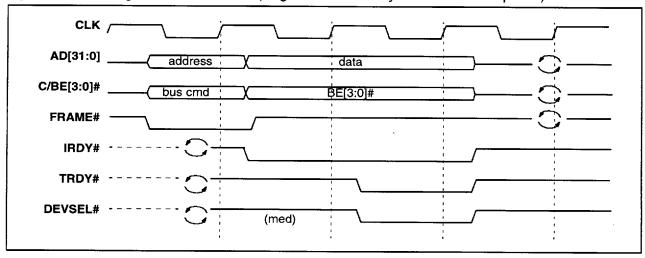

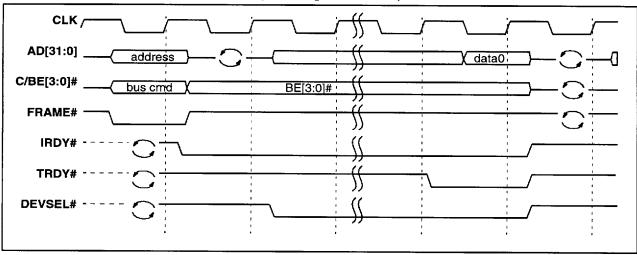

Figure 3. PCI Target write - Slave Write (single 32-bit with 1-cycle DEVSEL# response)

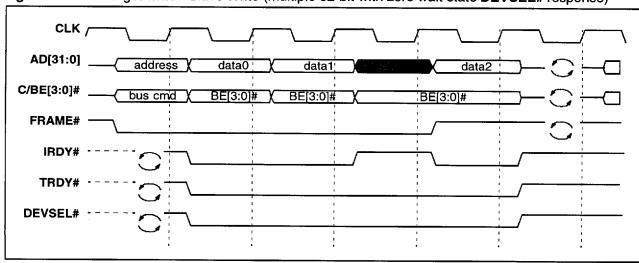

Figure 4. PCI Target write - Slave Write (multiple 32-bit with zero wait state DEVSEL# response)

14/81

7929237 0081594 011 **— — XY MARKET REPORTS**

<sup>1</sup> REQ# and GNT# are point to point signals and have different valid delay and input setup times than bussed signals. All other signals are bussed.

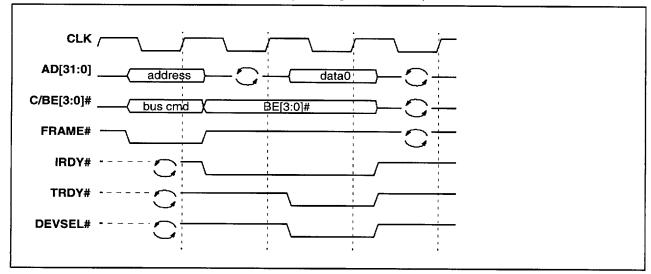

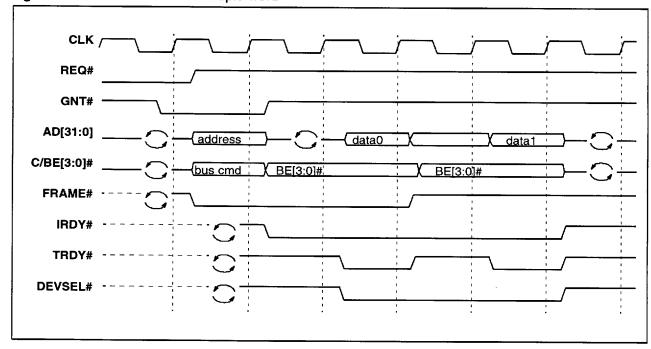

Figure 5. PCI Target read - Slave Read (1-cycle single word read)

Figure 6. PCI Target read - Slave Read (slow single word read)

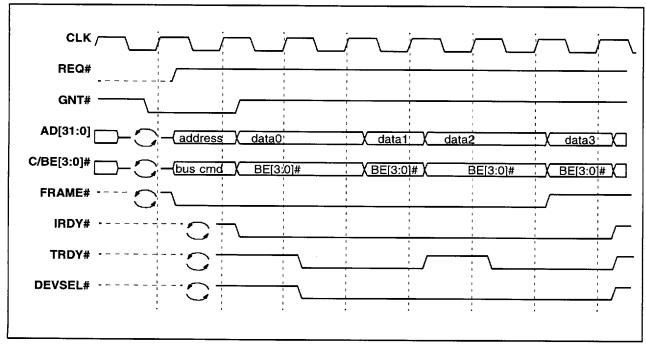

Figure 7. PCI Master write - multiple word

Figure 8. PCI Master read - multiple word

Note: The STG2000 does not generate fast back to back cycles as a bus master

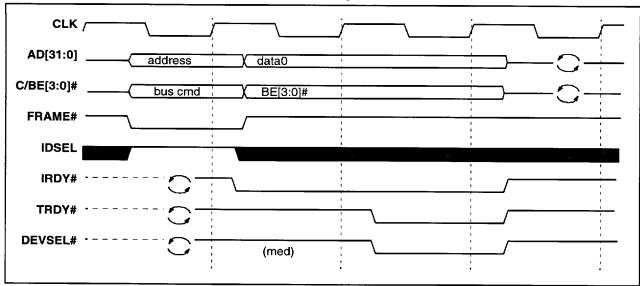

Figure 9. PCI Target configuration cycle - Slave Configuration Write

Figure 10. PCI Target configuration cycle - Slave Configuration Read

Figure 11. PCI basic arbitration cycle

Figure 12. Target initiated termination

18/81 — **SGS-THOMSO** ■ 7929237 0081598 767 ■

# 5 MEMORY AND PALETTE-DAC INTERFACE

#### 5.1 DRAM MEMORY INTERFACE

The STG2000 DRAM memory interface is designed primarily for 4Mbit, symmetric address 256K×16, dual CAS# memory devices. The following DRAM memory cycles are supported by the STG2000:

- Random read (non-page mode access)

- Random read with extended data output

- Random write (non-page mode access)

- Fast page-mode read

- Hyper page-mode read with extended data output

- Page-mode write (late write)

- Page-mode write with non-persistent writeper-bit mask

- CAS-before-RAS refresh

The STG2000 can access pixels as 8-bit, 16-bit or 32-bit wide values. The DRAM allocated to the frame buffer is therefore configured to be addressed uniformly in either 8-bit, 16-bit or 32-bit quantities.

The STG2000 memory controller internally generates its own refresh timer. It will request a refresh cycle every 776 MCLK periods. At 50MHz, this represents a refresh request rate of 15.52 $\mu$ s. The refresh operation is exclusively performed by CAS-before-RAS DRAM refresh cycles.

#### **DRAM** memory configurations

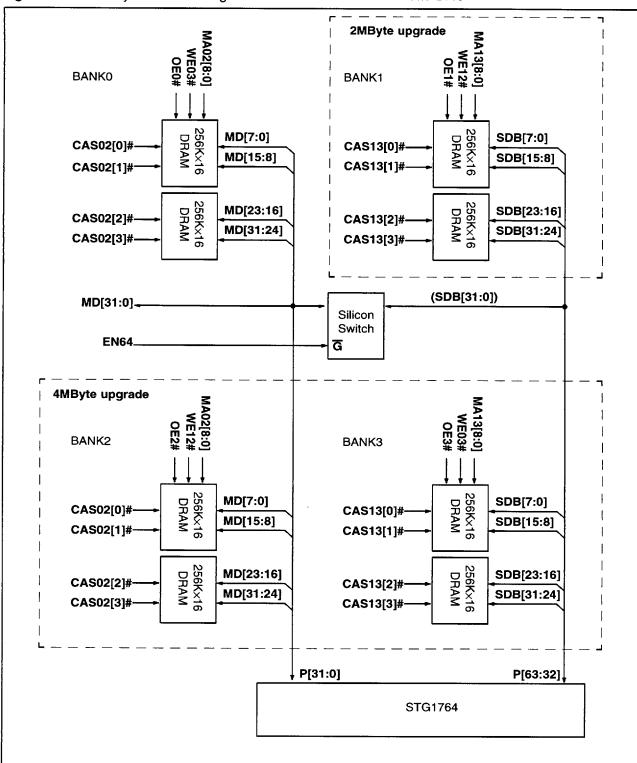

The STG2000 memory is organized in banks. A memory system consists of one, two, or four banks of DRAM. Each bank consists of two 256K×16 DRAMs comprising 1MByte of storage organized as 256K×32. The STG2000 memory interface comprises a 32-bit DRAM data bus, two 9-bit DRAM address buses and the control signals required to manage up to 4 banks of memory with a 2-to-1 interleave. Figure 13 shows memory interface options for 1, 2 and 4MBytes of DRAM.

The STG2000 supports hyper page mode (extended data output) cycles in some configurations. They include 1MByte with either the STG 1732 or STG1764 DAC, and both 2MByte and 4MByte with the STG1764. The advantage is that very high data transfer rates can occur when using the EDO DRAMs. Bursts from a 64-bit wide EDO memory into the STG1764 occur at up to 400MByte/s. Bursts from a 32-bit 1MByte EDO memory into the STG1732 occur at 200MByte/s.

Standard DRAM is interleaved for improved performance in a 32-bit (STG1732) 2MByte design. This provides a 200MByte/s data transfer rate. Standard 4MByte DRAM designs are also interleaved into the STG1764 at a data transfer rate of 200MByte/s. A 1MByte standard DRAM memory can achieve a 100MByte/s data transfer rate.

STG2000 256kx16 STG1732 STG2000 BANK 0 BANK0 One bank, non interleaved, 1MByte, 32-bit DAC STG1732 256kx16 BANK1 Two banks, interleaved, 2MByte, 32-bit DAC STG2000 BANKO silicon STG1764 switch 32 256kx16 BANK2 BANK1 Two banks, interleaved, 2MByte, 64-bit DAC STG2000 BANK0 silicon STG1764 switch 256kx16 BANK<sub>1</sub> 256kx16 32 **BANK3** Four banks, interleaved, 4MByte, 64-bit DAC

Figure 13. 1, 2 and 4MByte DRAM memory configuration options

Figure 14. 1-2MByte DRAM configuration with the STG1732 Palette-DAC

Figure 15. 1-4MByte DRAM configuration with the STG1764 Palette-DAC

## **DRAM** interface timing specification

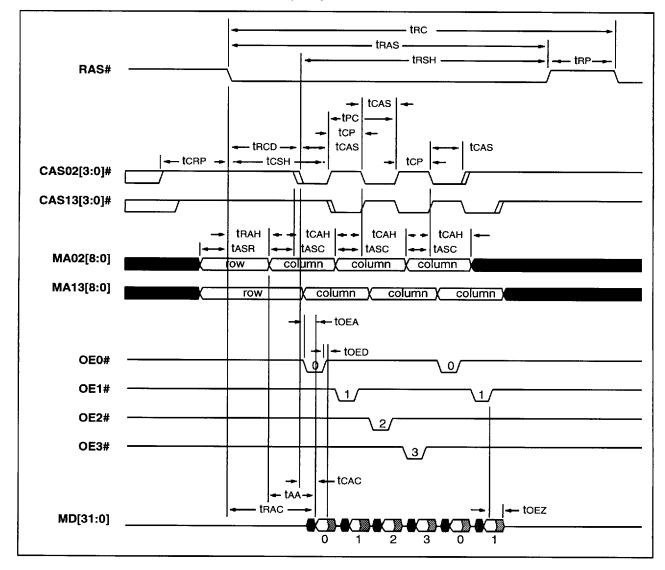

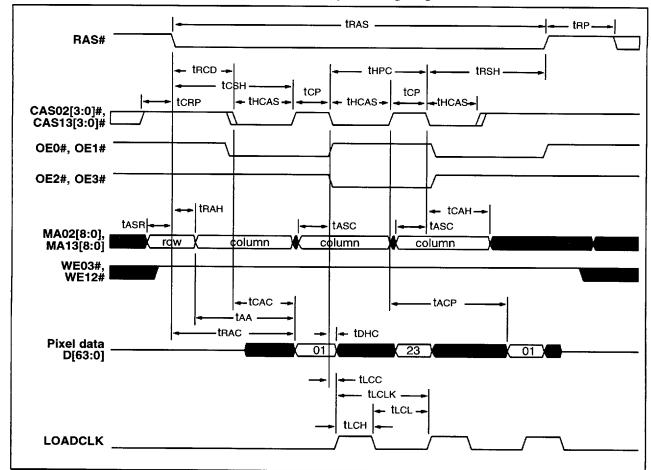

Figure 16. 4MByte DRAM read cycle timing diagram

Table 3. 4MByte DRAM read cycle timing parameters

| Symbol | Parameter                              | Min.       | Max. | Unit | Notes         |

|--------|----------------------------------------|------------|------|------|---------------|

| tRC    | Read cycle time                        | 6Тмсцк-5   |      | ns   |               |

| tras   | RAS# pulse width                       | 3.5TMCLK-2 |      | ns   |               |

| tRP    | RAS# precharge time                    | 2.5TMCLK-2 |      | ns   |               |

| tCRP   | CASxx[3:0]# to RAS# precharge time     | ЗТмсцк-10  |      | ns   |               |

| tcsн   | CASxx[3:0]# hold time                  | ЗТмськ-5   |      | ns   |               |

| tRCD   | RAS# to CASxx[0:3]# delay time         | 2TMCLK-5   |      | ns   |               |

| trsh   | RAS# hold time                         | 1.5TMCLK-2 |      | ns   |               |

| tCP    | CASxx[3:0]# precharge time (page mode) | TMCLK-5    |      | ns   |               |

| tCAS   | CASxx[3:0]# pulse width                | TMCLK-2    |      | ns   |               |

| tasr   | Row address setup time                 | 2          | -    | ns   |               |

| tasc   | Column address setup time              | 2          |      | ns   |               |

| trah   | Row address hold time                  | TMCLK-5    |      | ns   |               |

| tCAH   | Column address hold time               | Тмськ-5    | -,-  | ns   |               |

| tcac   | Access time from CASxx[3:0]#           | TMCLK      |      | ns   | ····          |

| taa    | Access time from column address        | 2TMCLK-5   |      | ns   |               |

| trac   | Access time from RAS#                  | 3TMCLK-2   |      | ns   | · · · · · · · |

| tPC    | Fast page mode cycle time              | 2TMCLK-2   |      | ns   |               |

| tOEA   | Output enable time                     | TMCLK-7    |      | ns   | <del></del>   |

| tOED   | Output disable to data invalid         | 0          |      | ns   |               |

| tOEZ   | OEx# rising to MD[31:0] high-z         |            | 7    | ns   |               |

<sup>1</sup> TMCLK is the period of the internal memory clock.

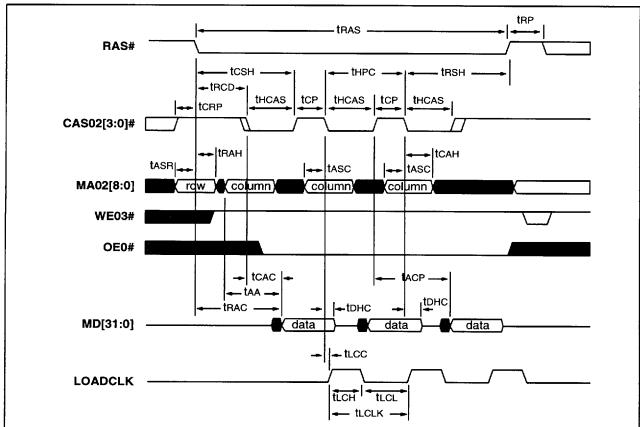

Figure 17. 1MByte DRAM hyper page mode read cycle timing diagram

Table 4. 1, 2 and 4MByte DRAM hyper page mode read cycle timing parameters

| Symbol | Parameter                                    | Min.       | Max.        | Unit | Notes |

|--------|----------------------------------------------|------------|-------------|------|-------|

| trc    | Read cycle time                              | 6TMCLK-5   |             | ns   |       |

| tras   | RAS# pulse width                             | 3.5TMCLK-2 |             | ns   |       |

| tRP    | RAS# precharge time                          | 2.5TMCLK-2 |             | ns   |       |

| tCRP   | CASxx[3:0]# to RAS# precharge time           | ЗТмськ-10  |             | ns   |       |

| tcsн   | CASxx[3:0]# hold time                        | ЗТмськ-5   |             | ns   | ***   |

| trcd   | RAS# to CASxx[0:3]# delay time               | 2TMCLK-5   |             | ns   |       |

| trsh   | RAS# hold time                               | Тмськ-2    |             | ns   |       |

| tCP    | CASxx[3:0]# precharge time (hyper page mode) | 0.5TMCLK-2 |             | ns   |       |

| tHCAS  | CASxx[3:0]# pulse width (hyper page mode)    | 0.5TMCLK-2 |             | ns   | 10.11 |

| tasr   | Row address setup time                       | 2          |             | ns   |       |

| tasc   | Column address setup time                    | 2          | <del></del> | ns   |       |

| tRAH   | Row address hold time                        | TMCLK-5    |             | ns   |       |

| tcah   | Column address hold time                     | TMCLK-5    | ***         | ns   |       |

| tCAC   | Access time from CASxx[3:0]#                 | TMCLK      | ···         | ns   | *     |

| taa    | Access time from column address              | TMCLK-2    |             | ns   |       |

| Symbol | Parameter                              | Min.       | Max. | Unit | Notes                                 |

|--------|----------------------------------------|------------|------|------|---------------------------------------|

| trac   | Access time from RAS#                  | 3Тмськ-2   |      | ns   |                                       |

| tHPC   | Hyper page mode read cycle time        | TMCLK-2    |      | ns   | · · · · · · · · · · · · · · · · · · · |

| tDHC   | Data hold from CASxx[3:0]#             | 2          |      | ns   | ***                                   |

| tACP   | Access time from CASxx[3:0]# precharge | 1.5TMCLK-5 |      | ns   | <del></del>                           |

| tLCH   | LOADCLK high pulse width               | 6          |      | ns   |                                       |

| tLCL   | LOADCLK low pulse width                | 6          |      | ns   |                                       |

| tLCK   | LOADCLK cycle time                     | 18         |      | ns   |                                       |

| tLCC   | LOADCLK rising from CASxx[3:0]# active |            | 0    | ns   | ***                                   |

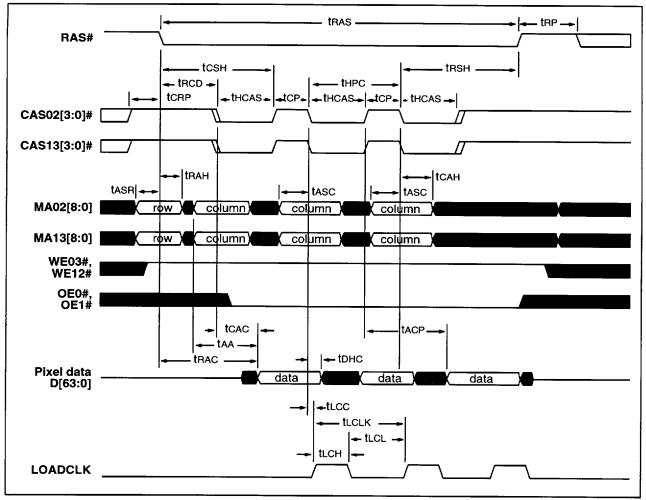

Figure 18. 2MByte DRAM hyper page mode read cycle timing diagram into STG1764

<sup>1</sup> TMCLK is the period of the internal memory clock.

<sup>1</sup> The timing parameters for the 2MByte DRAM hyper page mode read cycle are given in Table 4.

Figure 19. 4MByte DRAM hyper page mode read cycle timing diagram into STG1764

<sup>1</sup> The timing parameters for the 4MByte DRAM hyper page mode read cycle are given in Table 4.

tras tRC . -tRCD -tRP. RAS# tCAS tCP -tcsH tcas tcas -CAS02[3:0]# CAS13[3:0]# trah tasc tasc **t**ASC **tCAH** tCAH tCAH tasr MA02[8:0] column column column MA13[8:0] row column column column WE03# <u>ر</u>م - tcwL tRWL WE12# OE0#, OE1# OE2#, OE3# <del>--</del>tDH MD[31:0] data data data data

Figure 20. 4MByte DRAM write cycle timing diagram (MA02[8:0] and MA13[8:0] interleaved)

Table 5. 4MByte DRAM late write cycle timing parameters

| Symbol | Parameter                              | Min.       | Max. | Unit | Notes |

|--------|----------------------------------------|------------|------|------|-------|

| tRC    | Write cycle time                       | 6TMCLK-5   |      | ns   |       |

| tras   | RAS# pulse width                       | 3.5TMCLK-2 |      | ns   |       |

| trp    | RAS# precharge time                    | 2.5TMCLK-2 |      | ns   |       |

| tCRP   | CASxx[3:0]# to RAS# precharge time     | 3TMCLK-10  |      | ns   | _     |

| tcsн   | CASxx[3:0]# hold time                  | ЗТмськ-5   |      | ns   |       |

| trcd   | RAS# to CASxx[0:3]# delay time         | 2TMCLK-5   |      | ns   |       |

| trsh   | RAS# hold time                         | 1.5TMCLK-2 |      | ns   |       |

| tCP    | CASxx[3:0]# precharge time (page mode) | TMCLK-5    |      | ns   |       |

| tcas   | CASxx[3:0]# pulse width (page mode)    | TMCLK-2    |      | ns   |       |

| tasr   | Row address setup time                 | 2          |      | ns   |       |

| tasc   | Column address setup time              | 2          |      | ns   |       |

| trah   | Row address hold time                  | TMCLK-5    |      | ns   |       |

28/81 — **SGS-THOMSON** — 7929237 0081608 436

| Symbol | Parameter                                    | Min.       | Max.          | Unit | Notes |

|--------|----------------------------------------------|------------|---------------|------|-------|

| tCAH   | Column address hold time                     | TMCLK-5    |               | ns   |       |

| tPC    | Fast page mode cycle time                    | 2TMCLK-2   |               | ns   |       |

| twp    | Write command pulse width                    | 0.5TMCLK   |               | ns   | - ,   |

| tcwL   | Write command active to CASxx[3:0]# inactive | 0.5TMCLK+2 | <del>" </del> | ns   |       |

| tRWL   | Write command active to RAS# inactive        | 0.5TMCLK+2 |               |      |       |

| tDS    | Write data setup time                        | 0.5TMCLK-2 |               | ns   |       |

| tDH    | Write data hold time                         | 0.5TMCLK+2 |               | ns   |       |

1 TMCLK is the period of the internal memory clock.

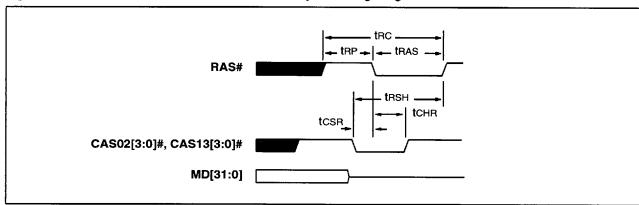

Figure 21. DRAM CAS# before RAS# refresh cycle timing diagram

Table 6. DRAM CAS# before RAS# refresh cycle timing parameters

| Symbol | Parameter                   | Min.       | Max. | Unit | Notes                                   |

|--------|-----------------------------|------------|------|------|-----------------------------------------|

| trc    | CAS# before RAS# cycle time | 6TMCLK-5   |      | ns   | *************************************** |

| tras   | RAS# pulse width            | 3.5TMCLK-2 |      | ns   |                                         |

| tRP    | RAS# precharge time         | 2.5TMCLK-2 |      | ns   |                                         |

| trsh   | RAS# hold time              | 4TMCLK-5   |      | ns   |                                         |

| tCSR   | CASxx[3:0]# setup time      | TMCLK-5    |      | ns   |                                         |

| tchr   | CASxx[3:0]# hold time       | TMCLK-5    |      | ns   |                                         |

## NOTE

1 TMCLK is the period of the internal memory clock.

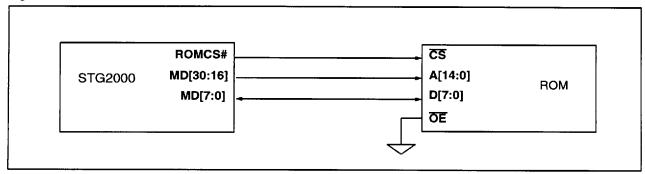

#### 5.2 ROM INTERFACE

BIOS and initialization code for the STG2000 is accessed from a 32KByte ROM.OTP or EPROM ROM may be selected The STG2000 memory bus interface signals **MDB[30:16]** and **MDB[7:0]** are used to address and read one of the 32KBytes of data respectively. The unique decode to the ROM device is provided by the **ROMCS#** chip select signal.

Figure 22. ROM interface

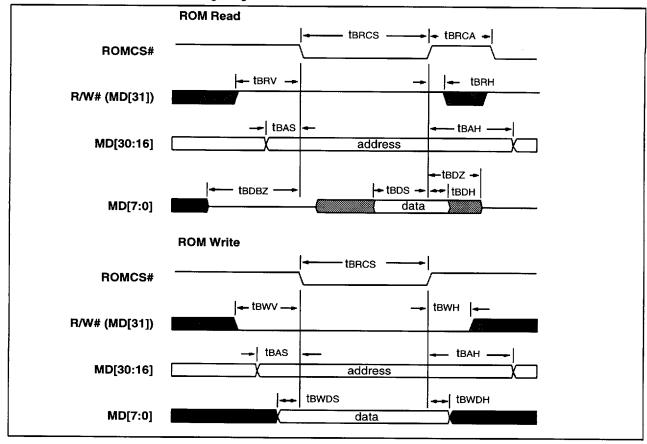

## ROM interface timing specification

Figure 23. ROM interface timing diagram

Table 7. ROM interface timing parameters

| Symbol | Parameter                             | Min.       | Max.    | Unit | Notes |

|--------|---------------------------------------|------------|---------|------|-------|

| tBRCS  | ROMCS# active pulse width             | 13TMCLK-5  |         | ns   |       |

| tBRCA  | ROMCS# precharge time                 | TMCLK-5    |         | ns   |       |

| tbrv   | Read valid to ROMCS# active           | TMCLK-5    |         | ns   |       |

| tBRH   | Read hold from ROMCS# inactive        | 0.5TMCLK-5 |         | ns   |       |

| tBAS   | Address setup to ROMCS# active        | TMCLK-5    |         | ns   |       |

| tBAH   | Address hold from ROMCS# inactive     | 0.5TMCLK-5 |         | ns   |       |

| tBDBZ  | Data bus high-z to ROMCS# active      | TMCLK-5    |         | ns   |       |

| tBDS   | Data setup to ROMCS# inactive         | 10         |         | ns   |       |

| tBDH   | Data hold from ROMCS# inactive        | 0          |         | ns   |       |

| tBDZ   | Data high-z from ROMCS# inactive      |            | TMCLK-5 | ns   |       |

| tewv   | R/W# valid setup to ROMCS# active     | TMCLK-5    |         | ns   |       |

| tBWH   | R/W# hold from ROMCS# inactive        | 0.5Тмсцк-5 |         | ns   |       |

| tBWDH  | Write data hold from ROMCS# inactive  | 0.5TMCLK-5 |         | ns   |       |

| tBWDS  | ROM write data setup to ROMCS# active | TMCLK-5    |         | ns   |       |

NOTE

7929237 0081611 T20 🖿 \_ 🕶 SGS-THOMSON

31/81

<sup>1</sup> TMCLK is the period of the internal memory clock.

#### 5.3 EEPROM INTERFACE

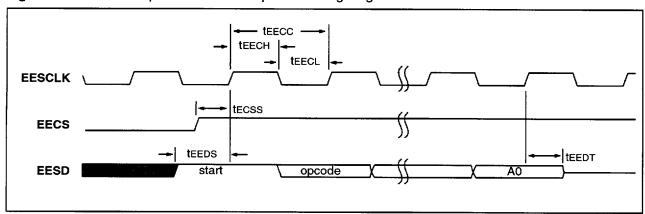

The STG2000 interface to the EEPROM is implemented via an industry standard Microwire bus. This 3-signal protocol uses a chip enable (EECS) to select the EEPROM. Data transfer is accomplished via a bidirectional serial data line (EESD) and clock (EESCLK).

The EEPROM is structured in a 128×8-bit word organization, such as the ST93C46A. This common format is available in a small outline (SO8) package which can easily be located in close proximity to the STG2000. The serial data transfer rate is low (<1MHz), hence signal routing is not critical. Details of the standard data format

structure and software interface protocol for accessing the 1Kbit data are given in the SGS-THOMSON Datasheet for the ST93C46A [7]. Preprogrammed EEPROM devices for the STG2000 Multimedia Accelerator chipset are available from SGS-THOMSON with the part number NVCAATR.

The STG2000 automatically unlocks the EE-PROM prior to sending a WRITE command. Following the write command it waits for the data line to be driven high, indicating completion of the write by the EEPROM. It then ends the user write request by sending an EWDS sequence to lock the EEPROM.

Figure 24. EEPROM power-on read sequence timing diagram

Table 8. EEPROM power-on read sequence timing parameters

| Symbol | Parameter                    | Min. | Max. | Units | Notes |

|--------|------------------------------|------|------|-------|-------|

| tEECC  | EESCLK period                | 50   |      | TMCLK |       |

| tEECH  | EESCLK high time             | 24   |      | TMCLK |       |

| tEECL  | EESCLK low time              | 24   |      | TMCLK |       |

| tECSS  | EECS high to EESCLK high     | 15   |      | TMCLK |       |

| tEEDS  | EESD valid to EESCLK high    | 15   |      | TMCLK |       |

| tEEDT  | EESCLK high to EESD inactive | 15   |      | TMCLK |       |

NOTE

1 TMCLK is the period of the internal memory clock.

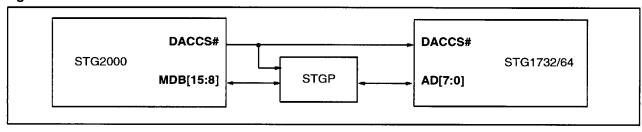

#### 5.4 PALETTE-DAC INTERFACE

The STG1764 or STG1732 Palette-DAC interface comprises an 8-bit multiplexed address/data bus connecting to MDB[15:8] of the STG2000 memory bus. The unique decode to the Palette-DAC is provided by the DACCS# chip select signal. Each access is split into two phases; address and data.

In the address phase the falling edge of **DACCS#** latches the 4-bit address into the Palette-DAC and latches **MDB[15]** (Palette-DAC signal **AD[7])** to identify whether the current access is a read or write.

Figure 25. DAC interface

## Palette-DAC interface timing specification

Figure 26. BLANK# timing diagram

Table 9. BLANK# timing parameters

| Symbol | Parameter          | Min. | Max. | Units | Notes |

|--------|--------------------|------|------|-------|-------|

| tBKS   | BLANK# set-up time | 4.0  |      | ns    |       |

| tBKH   | BLANK# hold time   | 4.0  |      | ns    |       |

DACCS# tSLAX towds tAVSL tshdx MD[11:8] RS[3:0] register select D[3:0] WRITE: MD[15:12] OXXX D[7:4] data tsHQX tsLQV tSLAZ | tsHQZ MD[11:8] D[3:0] data READ: register select MD[15:12] 1XXX D[7:4] read data bus turn

Figure 27. Palette-DAC interface read/write cycle timing diagram

Table 10. Palette-DAC interface read/write cycle timing parameters

| Symbol | Parameter                                | Min.        | Max.        | Unit | Notes                      |

|--------|------------------------------------------|-------------|-------------|------|----------------------------|

| tDP    | DAC interface precharge time             | 3TMCLK-5    |             | ns   | DAC write cycle            |

| tslsh  | DACCS# pulse time                        | ЗТмськ-5    |             | ns   | DAC read cycle             |

| tAVSL  | Address setup time                       | 1.5TMCLK-5  |             | ns   | Game Port read/write cycle |

| tslax  | Address hold time                        | 0           |             | ns   | All accesses               |

| towds  | Write data setup time                    |             | 0.5TMCLK+10 | ns   | Write cycle                |

| tshdx  | Write data hold time                     | 0.5TMCLK-10 |             | ns   | Write cycle                |

| tSLAZ  | Address high-z time                      |             | 10          | ns   | Read cycle                 |

| tslqv  | Read access time from DACCS# active      | 2TMCLK-10   |             | ns   | Read cycle                 |

| tshqx  | Read data hold time from DACCS# inactive | 0           | .,          | ns   | Read cycle                 |

| tsHQZ  | Output turn-off delay                    |             | TMCLK-5     | ns   | Read cycle                 |

1 TMCLK is the period of the internal memory clock.

#### 5.5 ALTCS# INTERFACE

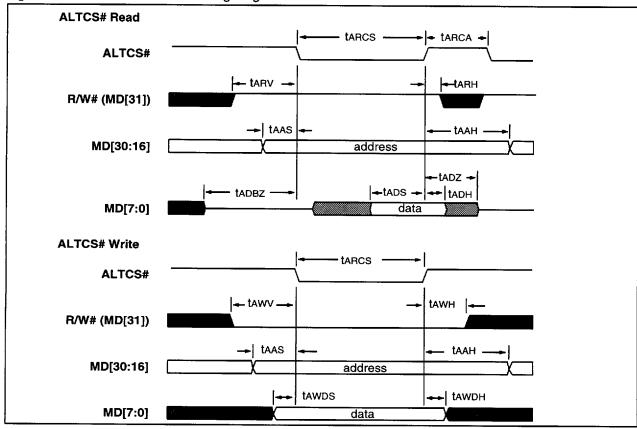

The STG2000 can access 32KBytes of read/write memory. The STG2000 memory bus interface signals MDB[30:16] and MDB[7:0] are used to address and access one of the 32KBytes of data respectively. MDB[31] provides an indication of a read or write cycle. The unique decode to this 32KByte device is provided by the ALTCS# chip select signal.

Figure 28. ROM interfaces

## **ALTCS# interface timing specification**

Figure 29. ALTCS# interface timing diagram

Table 11. ALTCS# interface timing parameters

| Symbol | Parameter                            | Min.       | Max.    | Unit | Notes |

|--------|--------------------------------------|------------|---------|------|-------|

| tarcs  | ALTCS# pulse width                   | 13TMCLK-7  |         | ns   |       |

| tARCA  | ALTCS# precharge time                | TMCLK-5    |         | ns   |       |

| tarv   | Read valid to ALTCS# active          | TMCLK-5    |         | ns   |       |

| tarh   | Read hold from ALTCS# inactive       | 0.5TMCLK-5 |         | ns   |       |

| taas   | Address setup to ALTCS# active       | TMCLK-5    |         | ns   |       |

| taah   | Address hold from ALTCS# inactive    | 0.5TMCLK-5 |         | ns   |       |

| tadbz  | Data bus high-z to ALTCS# active     | TMCLK-5    |         | ns   |       |

| tads   | Data setup to ALTCS# inactive        | 10         |         | ns   |       |

| tadh   | Data hold from ALTCS# inactive       | 0          | ··      | ns   |       |

| tADZ   | Data high-z from ALTCS# inactive     |            | TMCLK-5 | ns   |       |

| tawv   | R/W# valid setup to ALTCS# active    | TMCLK-5    |         | ns   |       |

| tawh   | R/W# hold from ALTCS# inactive       | 0.5TMCLK-5 |         | ns   |       |

| tawdh  | Write data hold from ALTCS# inactive | 0.5TMCLK-5 |         | ns   |       |

| tawds  | Write data setup ALTCS# active       | TMCLK-5    |         | ns   |       |

<sup>1</sup> TMCLK is the period of the internal memory clock.

| 36/81            |         |     | ccc         |  |

|------------------|---------|-----|-------------|--|

| <b>■</b> 7929237 | 0081616 | 502 | SGS-THOMSON |  |

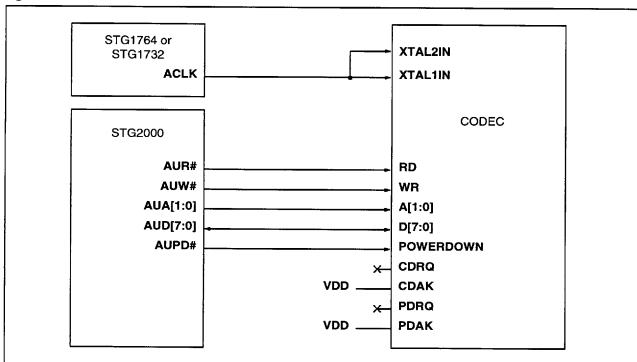

#### 6 AUDIO CODEC INTERFACE

The audio codec interface supports the Analog Devices AD1848 or equivalent. This is a mixed signal device that provides 16-bit stereo, multiple source audio capture and playback capability. The STG2000 audio codec interface, shown in Figure 30, does not use the interrupt or DMA features of the codec. The interface comprises an 8-bit data

bus, two address bits and independent read and write strobes. The codec may be placed in a power-saving mode by asserting AUPD#.

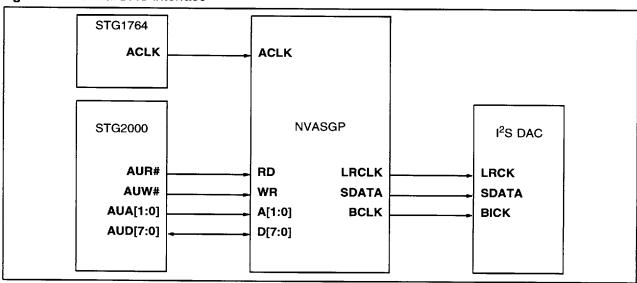

The interface for designs using the NVASGP ASIC and I<sup>2</sup>S DAC is shown in Figure 31.

Figure 30. Audio codec interface

Figure 31. Serial DAC interface

■ 7929237 0081617 449 ■ \_ SGS-THOMSON \_\_\_\_\_ 37/81

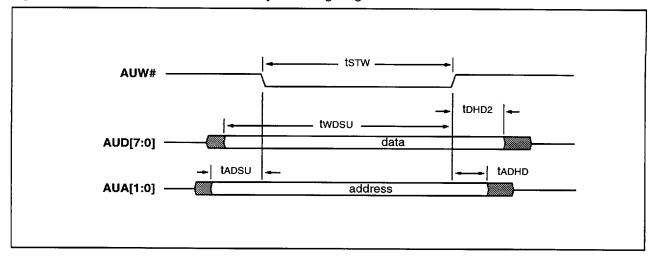

#### 6.1 AUDIO CODEC INTERFACE TIMING SPECIFICATION

Figure 32. Audio codec interface write cycle timing diagram

Table 12. Audio codec interface write cycle timing parameters

| Symbol | Parameter                      | Min.       | Max.   | Unit | Notes |  |

|--------|--------------------------------|------------|--------|------|-------|--|

| tstw   | AUW# strobe width              | 13TMCLK-10 |        | ns   | 1     |  |

| twosu  | AUD[7:0] setup to AUW# rising  | 17TMCLK-20 |        | ns   | 1     |  |

| tADSU  | AUA[1:0] setup to AUW# falling | 4TMCLK-20  |        | ns   | 1     |  |

| tadhd  | AUA[1:0] hold from AUW# rising | 3TMCLK-20  | t.b.d. | ns   | 1     |  |

| tDHD2  | AUD[7:0] hold from AUW# rising | 7TMCLK-20  | t.b.d. | ns   | 1     |  |

#### NOTE

<sup>1</sup> TMCLK = period of the internal memory clock

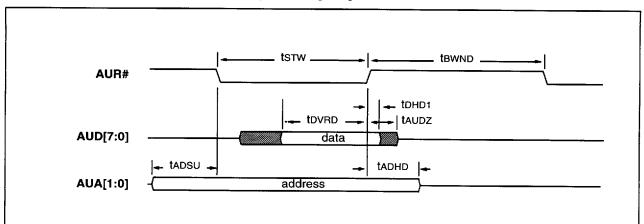

Figure 33. Audio codec interface read cycle timing diagram

Table 13. Audio codec interface read cycle timing parameters

| Symbol | Parameter                      | Min.       | Max.       | Unit | Notes<br>1 |  |

|--------|--------------------------------|------------|------------|------|------------|--|

| tstw   | AUR# strobe width              | 13TMCLK-10 |            | ns   |            |  |

| tBWND  | AUR# rising to AUR# falling    | 15TMCLK-10 | -          | ns   | 1          |  |

| tovrd  | AUD[7:0] valid to AUR# rising  | 20         | t.b.d.     | ns   |            |  |

| tadsu  | AUA[1:0] setup to AUR# falling | 4TMCLK-20  |            | ns   | 1          |  |

| tadhd  | AUA[1:0] hold from AUR# rising | 3Тмсцк-20  |            | ns   | 1          |  |

| tDHD1  | AUD[7:0] hold from AUR# rising | 0          |            | ns   |            |  |

| tAUDZ  | AUR# rising to AUD[7:0] high-z |            | 14TMCLK-20 | ns   | 1          |  |

#### NOTE

1 TMCLK = period of the internal memory clock

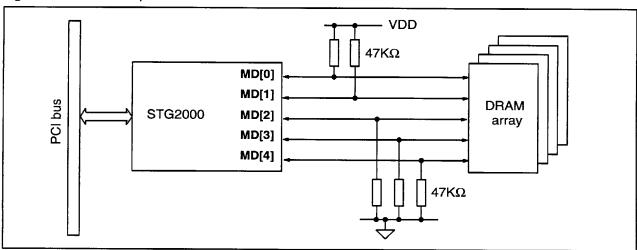

#### 7 POWER-ON RESET CONFIGURATION

The STG2000 latches its configuration on the trailing edge of RST#/RESET# and holds its system bus interface in a high impedance state until this time. Normally the configuration is read from the BIOS which is located on the memory data bus. The memory interface drives RAS# and OE# inactive during this period.

In motherboard designs the BIOS will typically be merged with that of the system, hence the configuration information must be transferred in another manner. To accomplish this, pull-up or pull-down resistors are connected to the **MD[7:0]** bus as appropriate. In the STG2000 only bits [4:0] are significant. Since there are no internal pull-up or pull-down resistors and the data bus should be floating during reset, a resistor value of  $47 \text{K}\Omega$  should be sufficient.

Figure 34. Planar implementation of STG2000 on the PCI bus

#### Power-on reset MD[7:0] bit assignments

| 7 | 6        | 5 | 4        | 3     | 2    | 1        | 0          |

|---|----------|---|----------|-------|------|----------|------------|

|   | Reserved |   | Bus Type | Board | Туре | Frame Bu | ıffer Type |

#### [7:5] Reserved

[4] Bus Type

0 = PCI bus

1 = VL-bus

[3:2] Board Type

00 = Motherboard

01 = Adapter #1 Note: Normally add-on cards will use the Adapter #1 configuration.

10 = Adapter #2

11 = Adapter #3

[1:0] Frame Buffer Type

00 = VRAM

01 = Illegal

10 = Illegal

11 = DRAM

#### 8 ELECTRICAL SPECIFICATIONS

#### 8.1 ABSOLUTE MAXIMUM RATINGS<sup>1</sup>

| Symbol | Parameter                        | Min.    | Max. | Units | Notes       |

|--------|----------------------------------|---------|------|-------|-------------|

| VDD    | DC supply voltage                |         | 3.6  | V     |             |

|        | Voltage on input and output pins | GND-1.0 | 7.5  | V     | <del></del> |

| TS     | Storage temperature (ambient)    | -55     | 125  | °C    |             |

| TA     | Temperature under bias           | 0       | 85   | °C    |             |

#### NOTE

#### 8.2 DC SPECIFICATIONS

Table 14. DC characteristics

| Symbol | Parameter                   | Min. | Тур. | Max. | Units | Notes |

|--------|-----------------------------|------|------|------|-------|-------|

| VDD    | Positive supply voltage     | 3.0  | 3.3  | 3.6  | V     |       |

| IIN    | Input current (signal pins) |      |      | ±10  | μΑ    | 1, 2  |

| PDmax  | Power dissipation           |      |      | 1.7  | W     |       |

#### **NOTES**

- 1 Includes high impedance output leakage for all bi-directional buffers with tri-state outputs

- 2 VDD = max, GND ≤ VIN ≤ VDD

Table 15. Parameters applying to VL-bus interface pins

| Symbol | Parameter                          | Min. | Тур. | Max. | Units | Notes                                            |

|--------|------------------------------------|------|------|------|-------|--------------------------------------------------|

| CIN    | Input capacitance                  |      | 10   | 12   | pF    |                                                  |

| COUT   | Output load capacitance            |      | 10   | 175  | pF    |                                                  |

| VIH    | Input logic 1 voltage              | 2.0  |      | 5.5  | V     |                                                  |

| VIL    | Input logic 0 voltage              | -0.5 |      | 0.8  | V     |                                                  |

| VOH    | Output logic 1 level               | 2.4  |      |      | V     | <u> </u>                                         |

| VOL    | Output logic 0 level               | ·    |      | 0.5  | V     |                                                  |

| IOL    | Output load current, logic 0 level |      |      | 8    | mA    | <del>                                     </del> |

Table 16. Parameters applying to PCI interface pins

| Symbol    | Parameter                            | Min.     | Тур. | Max.   | Units | Notes                                            |

|-----------|--------------------------------------|----------|------|--------|-------|--------------------------------------------------|

| CIN       | Input capacitance                    | 5        |      | 10     | pF    | <del>                                     </del> |

| COUT      | Output load capacitance              | 5        |      | 50     | pF    |                                                  |

| Parameter | s for 5V signaling environment only: |          |      |        |       |                                                  |

| VIH       | Input logic 1 voltage                | 2.0 5.75 |      | ٧      |       |                                                  |

| VIL       | Input logic 0 voltage                | -0.5     |      | 0.8    | V     |                                                  |

| VOH       | Output logic 1 level                 | 2.4      |      |        | V     |                                                  |

| VOL       | Output logic 0 level                 |          |      | 0.55   | V     |                                                  |

| IOH       | Output load current, logic 1 level   |          |      | -2     | mA    |                                                  |

| IOL       | Output load current, logic 0 level   |          |      | 3 or 6 | mA    | 1                                                |

■ 7929237 0081621 97T ■

- SGS-THOMSON

41/81

Stresses greater than those listed under 'Absolute maximum ratings' may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability.

## STG2000 rev. C

| Symbol    | Parameter                              | Min.     | Тур. | Max.         | Units | Notes    |

|-----------|----------------------------------------|----------|------|--------------|-------|----------|

| Parameter | s for 3.3V signaling environment only: |          |      | <del> </del> |       | 1        |

| VIH       | Input logic 1 voltage                  | 0.475VDD |      | VDD+0.5      | ٧     | T        |

| VIL       | Input logic 0 voltage                  | -0.5     |      | 0.325VDD     | V     | <b>1</b> |

| VOH       | Output logic 1 level                   | 0.9VDD   |      |              | V     |          |

| VOL       | Output logic 0 level                   |          |      | 0.1VDD       | V     |          |

| IOH       | Output load current, logic 1 level     |          |      | -0.5         | mA    |          |

| IOL       | Output load current, logic 0 level     |          |      | 1.5          | mA    |          |

NOTE

Table 17. Parameters applying to all signal pins except VL-bus and PCI interfaces

| Symbol | Parameter                          | Min. | Тур. | Max. | Units | Notes |

|--------|------------------------------------|------|------|------|-------|-------|

| CIN    | Input capacitance                  | ···· | 10   | 12   | pF    |       |

| COUT   | Output load capacitance            |      | 10   | 50   | pF    |       |

| VIH    | Input logic 1 voltage              | 2.0  |      | 5.75 | V     |       |